This equipment is a precise clock generator, able to provide programmable frequencies from 8KHz to 200MHz on three independent outputs.

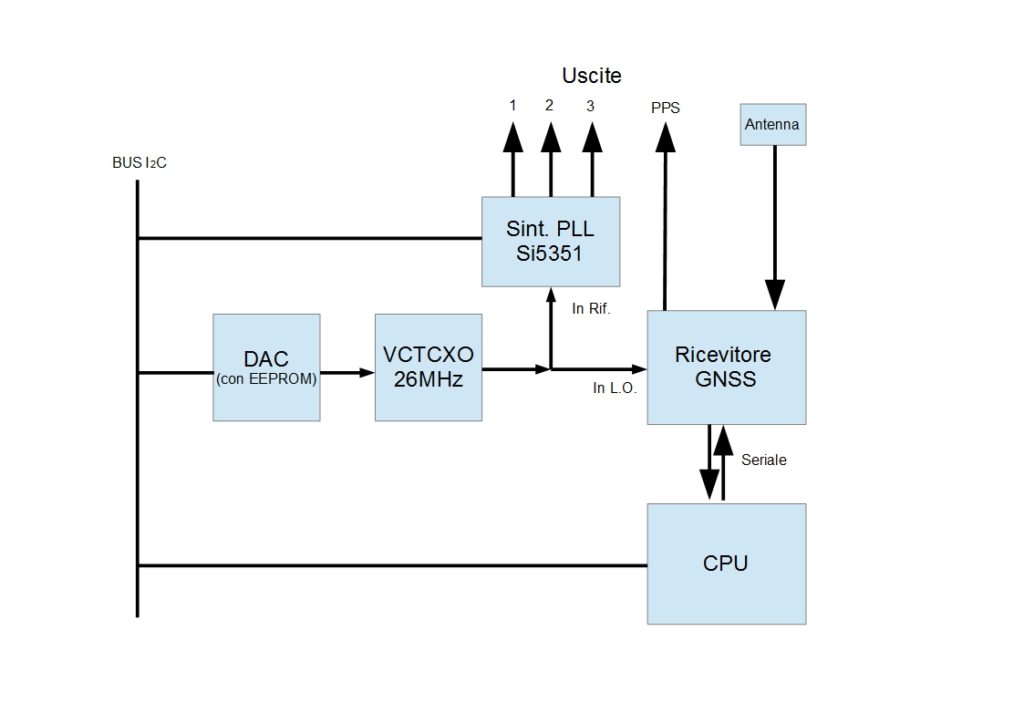

The generation of the signals is provided by a Si5351A. In this application, the Si5351A PLL uses as a reference a disciplined oscillator (GPSDO) based on the G7020-KT chip.

The control of GPSDO, PLL and the user interface (a 101X80 pixel color LCD and an encoder) is provided by an ATMega328P operating at 3.3V-8MHz.

Power is supplied by a 3.7V 600mA lpo battery which guarantees about four hours of use. The battery is connected to the step-up module which provides 5V for some modules and 3.3V through two LDOs via a CPU-controlled mosfet switch; the use of the mosfet guarantees the switching off of the appliance if the battery level drops. This switch circuit allows to have a quiescent current close to 0 uA. The charge and discharge control of the battery is also provided by the CPU and the TP4056/DW01A chips for charging and the overcharge protection and in additional overdischarge protection in the event of a CPU lock. The battery level is constantly displayed on the LCD, both during discharge and charging phases.

The “heart” of the generator is a VCTCXO oscillator which provides the reference to the G7020-KT GPS module and the Si5351A. The control voltage of the VCTCXO is given by a MCP4725 DAC (12bit resolution and I2C interface). The values sent to the DAC are processed by the CPU based on the feedback received from the GPS module about the offset of the reference oscillator with respect to the one hooked to the satellite. The CPU receives UBX messages about the Drift clock from the G7020-KT via a serial connection. The DAC is equipped with an internal EEPROM memory that allows the sending of the control voltage preset to VCTCXO at moment of power-up, to speed up the GPS syncronize.

From the user interface it is possible to set the frequencies and power levels of the three outputs of the Si5351, respectively with a resolution of 1Hz and with four different output levels; 0.76DBm, 7DBm, 10DBm and 12DBm. The equipment has also a fourth output in SMA, concerning the PPS output of the GPS module synthesizer, also this last output is programmable from the user interface in frequency from 1Hz to 24MHz (for an acceptable phase noise, use only 48MHz sub-multiples) and in duty cycle from 1% to 99%. It is possible to set the PPS active only during the GNSS sync, moreover it is also possible to set manually the value sent to the DAC, a useful function for example to speed up calibration in the event of VCTCXO replacement.

All the above settings can be saved in the EEPROM of the CPU so that after a few seconds from a subsequent restart, the equipment generates the frequencies with the saved settings.

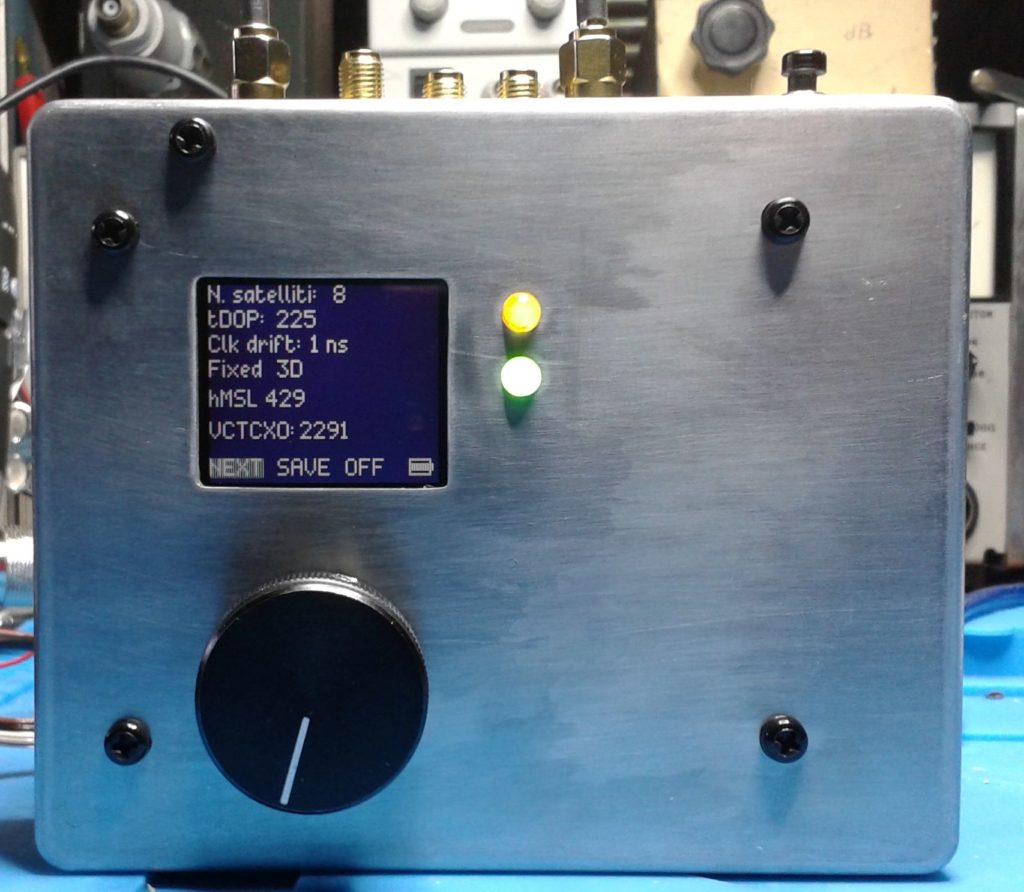

The yellow LED on the panel shows the PPS output signal negate (LED off = high signal), while the green LED indicates the correction operation performed on the VCTCXO: LED off = no GPS reception or PDO higher than 5 (minimum level to consider the clock drift), LED flashing = tDOP less than 5, clock drift above +/- 4ns and a correction of the VCTCXO voltage by the DAC is in progress, LED on steady = clock drift below +/- 5ns.

Finally, the following dynamically updated values are displayed on the GPS screen: number of satellites used, the DOP (time dilution of precision), the clock drift value expressed in ns (corresponding to an oscillator deviation of 0.026 Hz per unit ), the type of fixed none, 2D or 3D, the position in longitude and latitude and meters above sea level, date and time in UTC, and finally the value of the voltage sent by the DAC to the VCTCXO in the range from 0 to 4095 (in steps of about 0.8mv); the VCTCXO responds to the control voltage in a negative way, so as the voltage rises the frequency of the VCTCXO drops.